# Study on Division of Functions of In-Vehicle Architecture

# 1. Outline

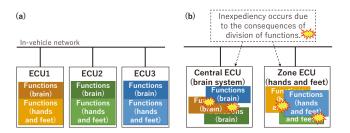

In the architecture of automotive electronic devices, functions have been conventionally implemented with discrete ECUs. The trend in these functions in the next-generation architecture, which is required to meet the needs for expandability and flexibility, is toward divided implementation into a brain (central ECU) in which control functions are integrated, and hands and feet (zone ECUs) that drive sensors and loads.

One challenge encountered when dividing functions into a central ECU and zone ECUs is that inexpediency occurring between functions is difficult to identify due to the complexity of the software structures involved, resulting in time-consuming architecture assessment (Fig. 1).

Addressing this challenge, AutoNetworks Technologies, Ltd. has leveraged models to improve the efficiency of problem identification and solution development during the process of division of functions.

This study has been adopted for joint research with an original equipment manufacturer in Japan.

## 2. Features

# 2-1 Ascertaining consequences by visualizing software structures

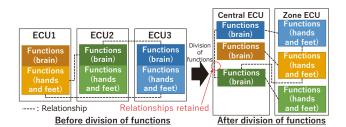

The use of a modeling language for describing functions previously implemented with design documentation and source code visualizes the relationships between functions by means of connectors (lines). These relationships are maintained even after the functions are divided into a central ECU and zone ECUs, enabling the scope of functional consequences to be elucidated even in an increasingly complex software structure (Fig. 2).

#### 2-2 Accelerated investigation due to tradeoff analysis

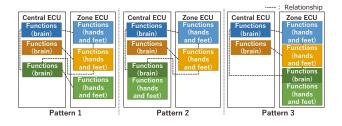

For a model in which functions are divided into central and zone ECUs, conceivable patterns of division of functions are developed (Fig. 3). Multiple patterns are compared with the relationships between functions in mind (tradeoff analysis), in addition to the confirmation of functional constraints identified in advance based on the requirements and specifications (Fig. 4). Thus it becomes possible to narrow down valid candidate architecture and to investigate efficient division of functions.

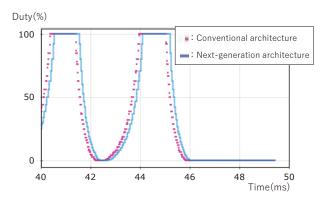

## 2-3 Verification by simulation

Selected candidate architecture models are verified by simulation. While verification items are diverse, including logical viability, electric current value, and processing time, this simulation can check the logical viability of control. For example, for a model depicting decorative illumination functions, the resultant outputs can be compared and checked as to whether they are permissible in an in-vehicle system, with the aim of ascertaining the consequences of communication time delays resulting from the division of functions (Fig. 5). Consequently, in in-vehicle architecture evolving in the future, by visualizing increasingly complex software structures, the current study helps ascertain the consequences of division of functions, and is expected to accelerate and improve the efficiency of architecture investigation.

Fig. 1. (a) conventional architecture and (b) next-generation architecture

Fig. 2. Retention of relationships after division of functions

Fig. 3. Development of patterns of division of functions

| Candidate architecture | Functional<br>constraint 1 | Functional<br>constraint 2 | Functional<br>constraint 3 | <br>Advantage                       | Disadvantage                    |

|------------------------|----------------------------|----------------------------|----------------------------|-------------------------------------|---------------------------------|

| Pattern 1              | ОК                         | NG                         | ОК                         | <br>OK : Updating                   | NG : Volume of<br>communication |

| Pattern 2              | ОК                         | ОК                         | ОК                         | <br>OK : Volume of<br>communication | NG : Delay in<br>output         |

| Pattern 3              | ОК                         | NG                         | NG                         | <br>OK : Vol te of                  | NG : Updating                   |

|                        |                            |                            |                            | <br>Valid candidates na             | rrowed down                     |

Fig. 4. Candidates narrowed down through tradeoff analysis

Fig. 5. Simulation comparing outputs of illumination functions